Status Signal In 8086 رسمه

During t1 it is low.

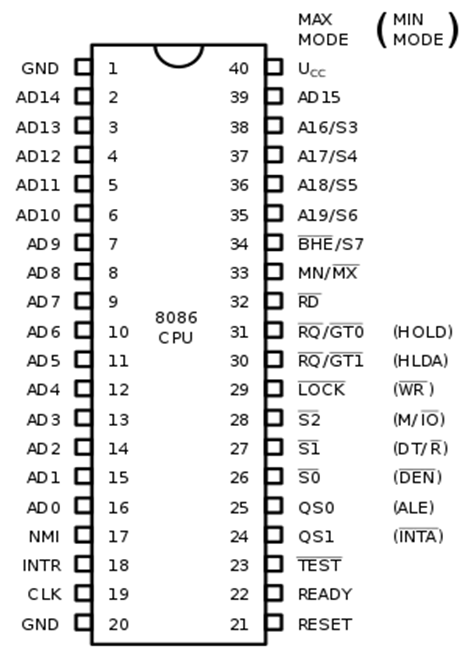

Status signal in 8086 رسمه. Instead it outputs three status signals s0 s1 s2 prior to the initiation of each bus cycle. It is an output signal activated by the lock prefix instruction and remains active until the completion of the instruction prefixed by lock. As shown in the fig. A status flags there are 6 flag registers in 8086 microprocessor which become set 1 or reset 0 depending upon condition after either 8 bit or 16 bit operation.

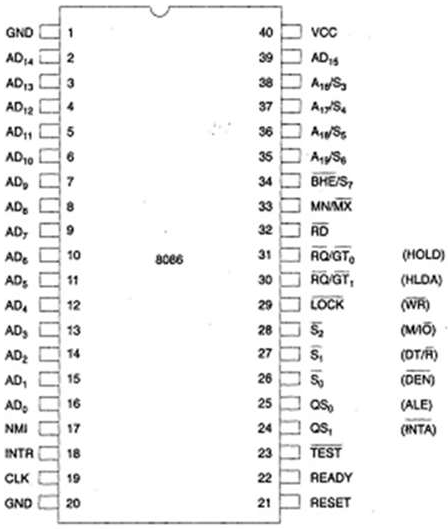

These flags are conditional status flags. The signal must be active high 1 for at least four clock cycles. It enables the data onto the most significant half of data bus d8 d15. Power supply 5v d c gnd.

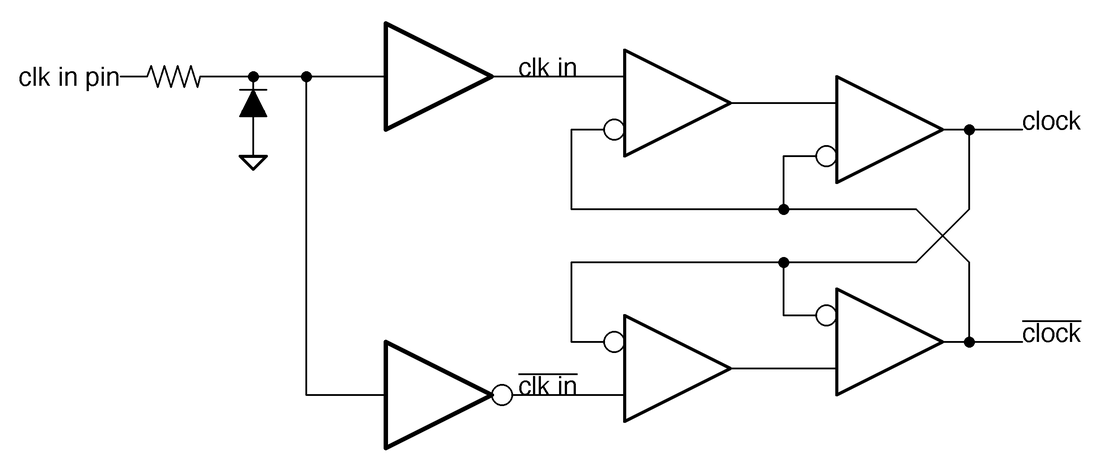

The 8086 while executing the prefixed instruction asserts the bus lock signal output which may be connected to an external bus controller. Qs 1 qs 0 queue status. When efi input is used csync signal is used for multiple buffered before it leaves the clock generator. These lines give information about the status of the code prefetch queue.

The processor provides the status of queue on these lines. Specially the wr m io dt r den ale and inta signals are no longer produced by the 8086. It is multiplexed with status signal s7. 10 5 the output of the divide by 3 counter generates the timing for ready synchronization a signal for another counter divide by 2 and the clk signal to the 8086 8088 microprocessors.

A19 is multiplexed with status signal s6. 5 of these flags are same as in case of 8085 microprocessor and their working is also same as in 8085 microprocessor. 8 bit device connected to upper half of the data bus use bhe signal. 8086 does not directly provide all the signals that are required to control the memory i o and interrupt interfaces.